Грень В.И., студент Курочкин В.О., студент Курочкин В.О., студент Кузнецов Н.А., старший преподаватель Кафедра информационных систем Кафедра компьютерных интеллектуальных систем и сетей Одесский Национальный Политехнический Университет

## ИССЛЕДОВАНИЕ СПЕЦИАЛИЗИРОВАННЫХ КОМПЬЮТЕРНЫХ СИСТЕМ НА БАЗЕ FPGA

В рамках исследования расмотрены вопросы повышения достоверности результатов работы утройств на базе FPGA при характерных неисправностях. Представлена среда для моделирования и отладки таблиц поиска (Look-up table - LUT).

Введение. Часто для разработки и исследования устройств, построенных с использованием таблиц поиска (Look-up table или LUT), необходимы сложные программные и аппаратные комплексы. Так для разработки устройств с использованием микросхем FPGA необходимо иметь саму микросхему, как аппаратное обеспечение для отладки проекта [1]. Также для более глубокой разработки нужно владеть информацией об описании таблиц поиска в конкретной среде проектирования. При разработке программных таблиц поиска ситуация еще хуже, так как не существует среды отладки для таблиц поиска, реализованных программным путем.

**Цель работы.** Целью исследования является создание актуальной системы моделирования и отладки таблиц поиска (Look-up table - LUT), позволяющей оценить повышение достоверности результатов работы устройств на базе FPGA при характерных неисправностях.

Основная часть работы. В процессе эксплуатации вычислительных устройств построенных на FPGA часто возникают характерные неисправности, такие как «закоротка», «константные неисправности», «заростание» блоков памяти нулями или единицами. В этой связи возникает задача оценки влияния неисправности на достоверноять окончательного результата выдаваемого устройством. Для решения данной задачи была разработана система анализа результов работы FPGA при характерных неисправностях [2].

Система позволяет задавать содержимое таблиц поиска (Look-up table - LUT), которые являются основой любого FPGA устройства. Разработчики ПЛИС

на FPGA используют в основном 4-х, 5-ти, 7-ми адресные LUT-ы [3-5]. Система позволяет смоделировать работу любого FPGA устройства построенного на базе N-адресного LUT-а.

В процессе разработки был создан набор классов, реализующих определенные функции системы. Каждый класс может использоваться отдельно внешними программами сторонних разработчиков, что увеличивает ценность системы.

В системе присутствует удобный функционал, позволяющий задавать содержимое LUT-ов, генерировать входные последовательности, задавать неисправности и вести автоматический анализ результатов моделирования.

Для примера возьмем задачу сортировки единиц в двоичном числе, состоящем из четырех разрядов. Имеем X = [x1, x2, x3, x4]. Например если  $X = 1011_2$ , то результат должен быть равен  $Y = [y1, y2, y3, y4] = 1110_2$ .

Таблица истинности работы данного устройства представлена в таблице 1. При этом сигналы X1, Y1- считаем старшими разрядами, а сигналы X4,Y4 – младшими разрядами.

Основная часть схемы данного устройства будет представлена на базе четырёх LUT, каждый из которых имеет 4-ре адресных входа. Первый LUT размещает значение выхода разряда Y1, второй Y2, третий Y3, четвёртый Y4.

В результате при поступления на вход 4-х адресных LUT-ов комбинации  $1011_2$ , в соответствии с таблицей истинности, на выходе появится комбинация  $1110_2$ , соответсвующая набору $\mathbb{N}$ 211.

| Набор  |    | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|--------|----|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| входы  | X1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

|        | X2 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0  | 0  | 1  | 1  | 1  | 1  |

|        | X3 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1  | 1  | 0  | 0  | 1  | 1  |

|        | X4 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0  | 1  | 0  | 1  | 0  | 1  |

| выходы | Y1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

|        | Y2 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

|        | Y3 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0  | 1  | 0  | 1  | 1  | 1  |

|        | Y4 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

Таблица 1 – Таблица истинности

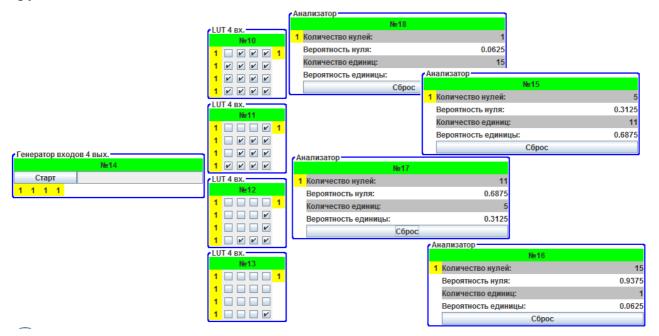

Схема на базе LUT и её анализ представлены на рисунке 1. Анализ схемы не составляет труда, как и ее построение. Начальный набор элементов системы будет расширятся. Так как элементы программы являются внешними классами и связь между ними организована с помощью независимых блоков входов и выходов, разработка операционных элементов сторонними разработчиками не составляет труда.

Рисунок 1— Анализ схемы сортировки единиц

Реализованная модель таблиц поиска обладает достаточной универсальностью и может применятся для моделирования булевых функций и стандартных логических элементов.

**Выводы.** Разработанная среда моделирования решает задачи построения схем с использованием таблиц поиска и анализа их работы. Таблицы поиска могут применятся для ускорения решения задач, требующих многоранговые комбинационные схемы, так как при любом наборе входных значений скорость выборки из таблицы постоянна и как правило достаточная для быстрого срабатывания устройства.

Востребованность программы напрямую зависит от необходимости использовать таблицы поиска. Так как технология FPGA основана на LUT, и является лидирующей на рынке, то и разработка подобного программного модуля не лишена смысла.

Использование программы не ограничивается анализом программных таблиц поиска или LUT в FPGA схемах. Благодаря открытому исходному коду и модульности разработанных компонентов систему легко можно дополнить нужным операционным элементом. При помощи стандартных элементов вполне возможно моделировать логические элементы и схемы, что является ценной возможностью в областях информационных технологий, связанных с использованием таблиц поиска.

Руководитель старший преподаватель ИКС Кузнецов Н.А.

## Литература

Грушвицкий Р.И. Проектирование систем на микросхемах с программируемой структурой / Р. И. Грушвицкий, А.Х. Мурсаев, Е.П. Угрюмов. – СПб.: БХВ, 2010. – 650 с.

Paul S. Reconfigurable Computing Using Content Addressable Memory for Improved Performance and Resource Usage / S. Paul, S. Bhunia // Proceedings of Design Automation Conference ACM/IEEE (DAC-2008). – Anaheim, 2008. – P. 786–791.

Maxfield C. The Design Warriors Guide to FPGAs: Design, Tools and Flows / C. Maxfield. – USA, Burlington: Newnes, 2004. – 542 p.

Дрозд Ю.В. Естественные ресурсы компьютерных систем на базе FPGA / Ю.В. Дрозд, А.В. Дрозд, Н.А. Кузнецов // Труды Одесского политехнического университета. – Одесса, 2013. – Вып. 2 (41). – С. 223–226.

Кузнецов Н.А. Метод повышения достоверности результатов, вычисляемых на FPGA / Н.А. Кузнецов, П.А. Якимов, Ю.В. Дрозд // Труды международной научно-практической конференции "Современные информационные и электронные технологии". – Одесса, 2012. – С. 94.